#### Cross-platform Open Security Stack for Connected Device

# D5.2 Integrated CROSSCON Security Stack - First Version

| Document Identification |       |                 |            |  |  |

|-------------------------|-------|-----------------|------------|--|--|

| Status                  | Final | Due Date        | 31/07/2024 |  |  |

| Version                 | 1.0   | Submission Date | 31/07/2024 |  |  |

| Related WP                | WP5                                         | Document Reference      | D5.2                                                   |

|---------------------------|---------------------------------------------|-------------------------|--------------------------------------------------------|

| Related<br>Deliverable(s) | D1.4, D1.6, D2.1, D3.1,<br>D3.2, D4.1, D4.2 | Dissemination Level (*) | PU                                                     |

| Lead Participant          | CYSEC                                       | Lead Author             | Yannick Roelvink                                       |

| Contributors              | 3MDEB, BIOT, TUD,<br>UMINHO, UWU            | Reviewers               | Ziga Putrle<br>(BEYOND)<br>Gergely Eberhardt<br>(SLAB) |

#### **Keywords:**

CROSSCON Stack Demonstrator, Integration, Use Case Prototypes

This document is issued within the frame and for the purpose of the CROSSCON project. This project has received funding from the European Union's Horizon Europe Programme under Grant Agreement No.101070537. The opinions expressed and arguments employed herein do not necessarily reflect the official views of the European Commission.

The dissemination of this document reflects only the author's view, and the European Commission is not responsible for any use that may be made of the information it contains. This deliverable is subject to final acceptance by the European Commission.

This document and its content are the property of the CROSSCON Consortium. The content of all or parts of this document can be used and distributed provided that the CROSSCON project and the document are properly referenced.

Each CROSSCON Partner may use this document in conformity with the CROSSCON Consortium Grant Agreement provisions.

(\*) Dissemination level: (PU) Public, fully open, e.g. web (Deliverables flagged as public will be automatically published in CORDIS project's page). (SEN) Sensitive, limited under the conditions of the Grant Agreement. (Classified EU-R) EU RESTRICTED under the Commission Decision No2015/444. (Classified EU-C) EU CONFIDENTIAL under the Commission Decision No2015/444. (Classified EU-S) EU SECRET under the Commission Decision No2015/444.

# **Document Information**

| List of Contributors   | List of Contributors |  |  |  |  |

|------------------------|----------------------|--|--|--|--|

| Name                   | Partner              |  |  |  |  |

| Yannick Roelvink       | CYSEC                |  |  |  |  |

| Emna Amri              | CYSEC                |  |  |  |  |

| Artur Raglis           | 3MDEB                |  |  |  |  |

| Tymoteusz Burak        | 3MDEB                |  |  |  |  |

| Shaza Zeitouni         | TUD                  |  |  |  |  |

| Ainara García Barinaga | BIOT                 |  |  |  |  |

| David Puron            | BIOT                 |  |  |  |  |

| David Cerdeira         | UMINHO               |  |  |  |  |

| Lukas Petzi            | UWU                  |  |  |  |  |

| Document | History    |                                                       |                                                                                                                                       |

|----------|------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Version  | Date       | Change editors                                        | Changes                                                                                                                               |

| 0.1      | 03/07/2024 | Yannick Roelvink                                      | Initial version, document layout definition and allocation of sections to contributors. Included first draft of Introduction chapter. |

| 0.2      | 15/07/2024 | Artur Raglis<br>Yannick Roelvink                      | Integration of first version of UC1 prototype sections, first version of Chapter 2 - CROSSCON Stack Development Progress.             |

| 0.3      | 16/07/2024 | Shaza Zeitouni                                        | Contribution to Chapter 2 & inclusion of UC5 prototype section.                                                                       |

| 0.4      | 17/07/2024 | Ainara García<br>Yannick Roelvink                     | Inclusion of UC2, UC3 & UC4 prototype sections.                                                                                       |

| 0.5      | 18/07/2024 | Yannick Roelvink                                      | Reformatting of UC descriptions, initial version of conclusion added submitted for internal review.                                   |

| 0.6      | 25/07/2024 | Yannick Roelvink<br>Emna Amri<br>David Puron          | Integrated comments from reviewers regarding<br>Chapters 1, 2, 3.2, 3.3 and 4.                                                        |

| 0.7      | 26/07/2024 | Yannick Roelvink<br>Shaza Zeitouni<br>Tymoteusz Burak | Integrated comments from reviewers regarding<br>Chapters 3.1, and 3.5                                                                 |

| 0.8      | 29/07/2024 | Yannick Roelvink                                      | Final version for QA.                                                                                                                 |

| 0.9      | 30/07/2024 | Juan Alonso                                           | Quality Assessment.                                                                                                                   |

| 1.0      | 31/07/2024 | Hristo Koshutanski                                    | Final version submitted.                                                                                                              |

| Quality Control     |                           |               |

|---------------------|---------------------------|---------------|

| Role                | Who (Partner short name)  | Approval Date |

| Deliverable leader  | Yannick Roelvink (CYSEC)  | 29/07/2024    |

| Quality manager     | Juan Alonso (ATOS)        | 30/07/2024    |

| Project Coordinator | Hristo Koshutanski (ATOS) | 31/07/2024    |

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                   |              |         | 2 of 33 |

|----------------|---------------------------------------------------------|-------------------|--------------|---------|---------|

| Reference:     | D5.2                                                    | Dissemination: PU | Version: 1.0 | Status: | Final   |

# Table of Contents

| Document Information                                                                          | 2    |

|-----------------------------------------------------------------------------------------------|------|

| Table of Contents                                                                             | 3    |

| List of Tables                                                                                | 4    |

| List of Figures                                                                               | 5    |

| List of Acronyms                                                                              | 6    |

| Executive Summary                                                                             | 7    |

| 1 Introduction                                                                                | 8    |

| 1.1 Purpose of the document                                                                   | 8    |

| 1.2 Relation to other project work                                                            |      |

| 1.3 Structure of the document                                                                 | 8    |

| 2 CROSSCON Stack Development Progress                                                         | 9    |

| 2.1 Status of CROSSCON Stack Components                                                       | 10   |

| 2.2 Status of CROSSCON Stack Trusted Services                                                 | 13   |

| 3 Use Case Integration Prototypes                                                             | 17   |

| 3.1 UC 1 - Device Multi-Factor Authentication                                                 | 17   |

| 3.1.1 Prototype Architecture                                                                  | 17   |

| 3.1.2 Required Security Features                                                              | 19   |

| 3.1.3 Integration Timeline                                                                    | 20   |

| 3.2 UC 2 - Firmware Updates of IoT Devices                                                    | 21   |

| 3.2.1 Prototype Architecture                                                                  | 21   |

| 3.2.2 Required Security Features                                                              | 22   |

| 3.2.3 Integration Timeline                                                                    | 22   |

| 3.3 UC 3 – Commissioning and Decommissioning of IoT Devices                                   | 23   |

| 3.3.1 Prototype Architecture                                                                  | 23   |

| 3.3.2 Required Security Features                                                              | 24   |

| 3.3.3 Integration Timeline                                                                    | 24   |

| 3.4 UC 4 - Remote Attestation for Identification and Integrity Validation of Agricultural UAV | s 25 |

| 3.4.1 Prototype Architecture                                                                  | 25   |

| 3.4.2 Required Security Features                                                              | 27   |

| 3.4.3 Integration Timeline                                                                    | 27   |

| 3.5 UC 5 - Intellectual Property Protection for Secure Multi-Tenancy on FPGA                  | 28   |

| 3.5.1 Prototype Architecture                                                                  | 28   |

| 3.5.2 Required Security Features                                                              | 30   |

| 3.5.3 Integration Timeline                                                                    | 31   |

| 4 Conclusions                                                                                 | 32   |

| References                                                                                    |      |

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                       |    |          | Page: | 3 of 33 |       |

|----------------|---------------------------------------------------------|-----------------------|----|----------|-------|---------|-------|

| Reference:     | D5.2                                                    | <b>Dissemination:</b> | PU | Version: | 1.0   | Status: | Final |

# List of Tables

| Table 1: Progress overview of CROSSCON Stack components       | 10 |

|---------------------------------------------------------------|----|

| Table 2: Progress overview of CROSSCON Stack trusted services | 13 |

| Table 3: Integration timeline for UC 1                        | 20 |

| Table 4: Integration timeline for UC 2                        |    |

| Table 5: Integration timeline for UC 3                        |    |

| Table 6: Integration timeline for UC 4                        |    |

| Table 7: Integration timeline for UC 5                        |    |

| Document name: | D5.2 Integrated C | 05.2 Integrated CROSSCON Security Stack - First Version |    |          |     | Page:   | 4 of 33 |

|----------------|-------------------|---------------------------------------------------------|----|----------|-----|---------|---------|

| Reference:     | D5.2              | <b>Dissemination:</b>                                   | PU | Version: | 1.0 | Status: | Final   |

# List of Figures

| Figure 1: Detailed CROSSCON Stack architecture[3]                                        | 9         |

|------------------------------------------------------------------------------------------|-----------|

| Figure 2: MFA implementation prototype for low-end to high-end device authentication     | 17        |

| Figure 3: MFA implementation prototype for mutual authentication between two high-end de | evices.18 |

| Figure 4: Secure firmware update implementation prototype                                | 21        |

| Figure 5: Secure (de)commission of IoT devices implementation prototype                  | 23        |

| Figure 6: UC 4 prototype architecture & integration with CROSSCON Stack                  | 26        |

| Figure 7: CROSSCON FPGA-SoC architecture & components                                    | 28        |

| Figure 8: vFPGA partitions                                                               | 29        |

| Figure 9: UC 5 integration with the CROSSCON Stack                                       | 30        |

|                                                                                          |           |

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                       |    |          | Page: | 5 of 33 |       |

|----------------|---------------------------------------------------------|-----------------------|----|----------|-------|---------|-------|

| Reference:     | D5.2                                                    | <b>Dissemination:</b> | PU | Version: | 1.0   | Status: | Final |

# List of Acronyms

| Abbreviation / | Description                              |  |  |  |

|----------------|------------------------------------------|--|--|--|

| acronym        |                                          |  |  |  |

| API            | Application Programming Interface        |  |  |  |

| D5.2           | Deliverable number 2 belonging to WP5    |  |  |  |

| EC             | European Commission                      |  |  |  |

| FCU            | Flight Control Unit                      |  |  |  |

| FPGA           | Field Programmable Gate Arrays           |  |  |  |

| GNN            | Graph Neural Network                     |  |  |  |

| HW             | Hardware                                 |  |  |  |

| loT            | Internet of Things                       |  |  |  |

| IPC            | Inter-Process Communication              |  |  |  |

| MFA            | Multi-Factor Authentication              |  |  |  |

| MitM           | Man-in-the-Middle (cybersecurity attack) |  |  |  |

| ML             | Machine Learning                         |  |  |  |

| MPU            | Memory Protection Unit                   |  |  |  |

| MS5            | 5th Project Milestone                    |  |  |  |

| mTLS           | Mutual Transport Layer Security          |  |  |  |

| OS             | Operating System                         |  |  |  |

| PG             | Perimeter Guard                          |  |  |  |

| PUF            | Physical Unclonable Function             |  |  |  |

| RA             | Remote Attestation                       |  |  |  |

| REE            | Rich Execution Environment               |  |  |  |

| SoC            | System on Chip                           |  |  |  |

| SPMP           | S-mode Physical Memory Protection        |  |  |  |

| SRAM           | Static Random-Access Memory              |  |  |  |

| SW             | Software                                 |  |  |  |

| ТА             | Trusted Application                      |  |  |  |

| TEE            | Trusted Execution Environment            |  |  |  |

| UAV            | Unmanned Aerial Vehicle                  |  |  |  |

| UC             | Use Case                                 |  |  |  |

| vFPGA          | Virtual Field Programmable Gate Arrays   |  |  |  |

| VM             | Virtual Machine                          |  |  |  |

| WP             | Work Package                             |  |  |  |

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                       |    |          | Page: | 6 of 33 |       |

|----------------|---------------------------------------------------------|-----------------------|----|----------|-------|---------|-------|

| Reference:     | D5.2                                                    | <b>Dissemination:</b> | PU | Version: | 1.0   | Status: | Final |

### **Executive Summary**

Deliverable D5.2 details the effort performed regarding the integration of the CROSSCON Stack. This includes (1) an update of the development status of the CROSSCON Stack components and trusted services, on which the integration, testing and validation activities of WP5 depend, as well as (2) a detailed description of the use case implementation prototypes that will be integrated into the testbed defined in T5.1, as preparation of the testing and validation activities of T5.3 and T5.4.

Where available, the development status of the CROSSCON Stack is illustrated using a description of a component's or trusted service's technical functionality. In addition, for each of the Use Case prototypes, a detailed description of their implementation architecture and their required components, trusted services and interfaces of the CROSSCON stack will be provided. Furthermore, the deliverable will provide an initial timeline of the integration of each of the use cases into the testbed environment.

Deliverable D5.2 contributes to the accomplishment of milestone MS5 "First version of integrated CROSSCON Stack and extension primitives, and first version of business model and market proposition".

| Document name: D5.2 Integrated CROSSCON Security Stack - First Version |      |                   |          |     | Page:   | 7 of 33 |

|------------------------------------------------------------------------|------|-------------------|----------|-----|---------|---------|

| Reference:                                                             | D5.2 | Dissemination: PU | Version: | 1.0 | Status: | Final   |

### 1 Introduction

#### 1.1 Purpose of the document

This document provides a demonstration of the current operational functionality of the CROSSCON Stack. This is achieved by listing and demonstrating the development status of the Stack's components and trusted services required for the integration, testing and validation activities of WP5, as well as a detailed overview of each of the use case implementation prototypes and their required security features. In addition, based on the status of the CROSSCON Stack, a timeline of the integration of each of the use case prototypes into the testbed is provided. This is crucial, as these use case prototypes will be used as a first reference for the activities of T5.3 and T5.4, related to the security testing of the use cases and CROSSCON Stack validation, respectively.

#### 1.2 Relation to other project work

This document aims to summarize the overall status of the CROSSCON Stack. As such, it derives the use case descriptions and operational scenarios, used to define the use case implementation prototypes, from D1.4[1]. In addition, the implementation prototypes presented in this document will be validated according to the validation criteria provided in D1.6.

The CROSSCON Stack components, trusted services and extension primitives presented in this document are based on the definitions of the CROSSCON Stack as provided in D3.1[4] and D4.1[6], respectively. In addition, some of the technical demonstration descriptions provided in this document are based on the development advancements presented in D3.2[5] and D4.2[7].

The outputs of this document are necessary inputs for the security testing and validation of the use case prototypes, as defined in D5.3 & D5.4.

#### 1.3 Structure of the document

This document is structured in 3 major chapters. After this introductory chapter, Chapter 2 will provide an overview of the development progress of the CROSSCON Stack, detailing the status of each of its components and trusted services, as well as providing a demonstration of their functionality where available. Afterwards, Chapter 3 will provide a detailed overview of the use case integration prototypes, including their required security features, and an associated integration plan, split into sections for each of the use cases. Lastly, Chapter 4 will summarize the key conclusions of the work presented in this document.

| Document name: D5.2 Integrated CROSSCON Security Stack - First Version |      |                |    | Page:    | 8 of 33 |         |       |

|------------------------------------------------------------------------|------|----------------|----|----------|---------|---------|-------|

| Reference:                                                             | D5.2 | Dissemination: | PU | Version: | 1.0     | Status: | Final |

### 2 CROSSCON Stack Development Progress

This chapter provides an overview of the current development status of the CROSSCON Stack. In section 2.1, we present the status of the core components needed to realize the different instantiations of the CROSSCON, while in section 2.2, we describe the status of the high-level security function provided by the trusted services.

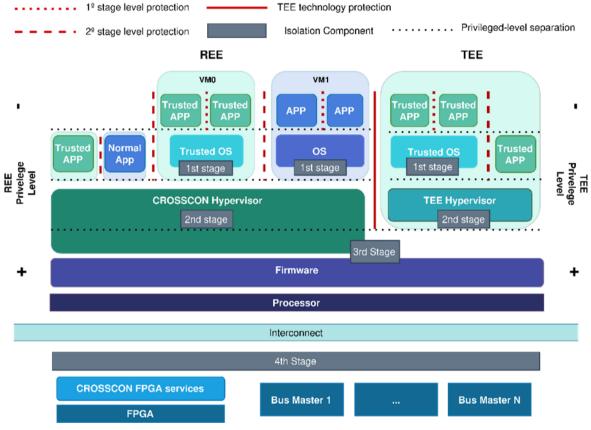

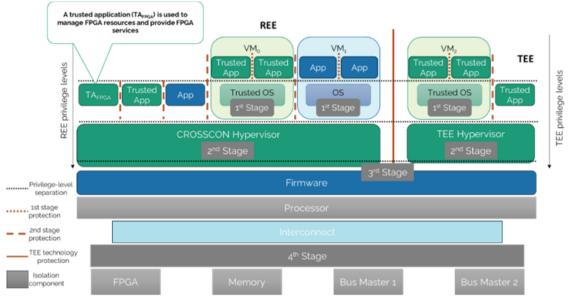

Figure 1, taken directly from D2.1[3], recalls the detailed architecture of the CROSSCON stack and its components.

Figure 1: Detailed CROSSCON Stack architecture[3]

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                       |    |          | Page: | 9 of 33 |       |

|----------------|---------------------------------------------------------|-----------------------|----|----------|-------|---------|-------|

| Reference:     | D5.2                                                    | <b>Dissemination:</b> | PU | Version: | 1.0   | Status: | Final |

#### 2.1 Status of CROSSCON Stack Components

Table 1 provides an overview of each of the CROSSCON Stack components' development progress, including a description of the component, its current integrability into the use case setups and a demonstration of its current technical capabilities, where available. For a more detailed description regarding each of the components, please refer to sections 3.2, 3.4 and 3.5 of D3.1[4]. For an overview of the code used for the technical demonstrations, please refer to D3.2[5] and D4.2[7].

| Component                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | Current Integration Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Technical Demonstration                                                                                                                                                                                                                                                                         |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CROSSCON<br>Hypervisor        | The CROSSCON Hypervisor is a static partitioning<br>Hypervisor that aims to provide strong isolation and<br>real-time guarantees. It is based on the Bao[8]<br>hypervisor, but implements additional features<br>such as (1) dynamic VM creation & management, (2)<br>per-VM TEE service support and (3) multiple Virtual<br>Machine Manager (VMM) support.                                                                    | Although the per-VM TEE service support has<br>been integrated and tested, the other two<br>features are still under development.<br>In addition, the CROSSCON Hypervisor is<br>currently only compatible with QEMU[9], an<br>open-source emulator used to virtualize<br>hardware platforms. While QEMU allows for<br>the testing of the Hypervisor and its<br>components prior to integration, work is<br>currently being performed to ensure<br>compatibility with several of the use case<br>hardware platforms required for integration. | Using the QEMU platform, the<br>CROSSCON Hypervisor is able to<br>demonstrate the ability to provide<br>per-VM TEE services, isolating the<br>TEE by running multiple TEE VMs<br>instead of a single TEE instance in the<br>normal world.                                                       |

| CROSSCON<br>bare metal<br>TEE | In order to still provide security for low-end systems<br>that are not compatible with the aforementioned<br>CROSSCON Hypervisor, CROSSCON proposes a<br>software-based bare-metal TEE, to allow bare-<br>metal devices to interact securely with the rest of<br>the CROSSCON Stack. The TEE will ensure the basic<br>security primitives such as memory isolation,<br>privilege separation and cross-domain<br>communication. | The bare-metal TEE has been integrated and<br>validated on both non-MPU and MPU devices.<br>Although both solutions provide a similar set<br>of security guarantees to deployed<br>applications, they do so using a slightly<br>different isolation mechanism.                                                                                                                                                                                                                                                                               | Two prototypes of the bare-metal<br>TEE are currently available: one<br>where the MPU version is<br>implemented on an ARMv7-M<br>architecture and another where the<br>non-MPU version is deployed on a<br>MSP430 architecture, both<br>illustrating the required basic security<br>primitives. |

#### Table 1: Progress overview of CROSSCON Stack components

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                   |              |         | 10 of 33 |

|----------------|---------------------------------------------------------|-------------------|--------------|---------|----------|

| Reference:     | D5.2                                                    | Dissemination: PU | Version: 1.0 | Status: | Final    |

| Component                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Current Integration Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Technical Demonstration |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                           | Two distinct versions of the bare-metal TEE are<br>being developed, one for bare-metal devices that<br>do not have a Memory Protection Unit (MPU), and<br>one for devices that do.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| CROSSCON<br>TEE Toolchain | <ul> <li>In order to manage the development and implementation of TEEs and TAs on the CROSSCON Stack, a toolchain is being developed that aims to support these activities.</li> <li>More specifically, the toolchain will be used to perform two critical tasks: <ul> <li>Secure IoT firmware updates: Based on the IETF proposed standard as detailed in RFC 9019 (SUIT), it allows for a secure mechanism to perform firmware updates on IoT devices[12].</li> <li>Secure cross-compilation of TAs for different TEEs: The toolchain will include a secure compiler, used to guarantee the memory safety of the TAs deployed on the TEEs within the CROSSCON Stack.</li> </ul> </li> </ul> | <ul> <li>The advancements of the TEE Toolchain can be grouped into three categories:</li> <li>Secure Update: The design for the secure firmware update feature is done, and the development for a first implementation is still ongoing. More information regarding this secure update mechanism can be found in D5.1</li> <li>Integration into DevSecOps: The toolchain will be integrated into the DevSecOps pipeline that will be used for the integration of the TAs onto the CROSSCON Hypervisor within the testbed environment of T5.1. This integration is currently still ongoing.</li> <li>Secure TA cross-compilation: The definition of a secure compiler, which takes code written from a simplified version of C to a memory safe version of the same code, has been performed. The implementation of this compiler, as well as the extension</li> </ul> | Not available           |

| Document name: | D5.2 Integrated C | ROSSCON Securit | y Stack - First Version |          |     | Page:   | 11 of 33 |

|----------------|-------------------|-----------------|-------------------------|----------|-----|---------|----------|

| Reference:     | D5.2              | Dissemination:  | PU                      | Version: | 1.0 | Status: | Final    |

| Component                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Current Integration Status                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Technical Demonstration                                                                                                                                                                                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | to lower programming languages, is currently ongoing.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                              |

| CROSSCON<br>SoC                | CROSSCON SoC <sup>1</sup> is a system-on-chip (SoC) design,<br>developed as part of the CROSSCON project, that<br>provides a secure RISC-V execution environment for<br>mixed-criticality IoT devices that require strong<br>security guarantees, flexibility, small code size and<br>low power consumption. The CROSSCON SoC<br>guarantees strong software isolation with the ability<br>to share hardware modules connected to the SoC<br>interconnect between TEEs without compromising<br>isolation guarantees. | A first implementation of the CROSSCON SoC<br>has been developed, designed around the<br>BA51-H core, which also integrates an<br>implementation of unified (2-stage) S-mode<br>Physical Memory Protection (SPMP) RISC-V<br>extension.<br>In addition, although a basic deployment is<br>already available, work is still being<br>performed to fully port the CROSSCON<br>Hypervisor on top of the BA51-H CROSSCON<br>SoC, in order to provide a full secure Stack<br>implementation. | The current implementation of the<br>CROSSCON SoC has successfully been<br>integrated with the BA51-H core, and<br>provides a Perimeter guard<br>demonstrator that allows one to<br>share the SRAM module between<br>isolated domains / VMs. |

| CROSSCON<br>Perimeter<br>Guard | A Perimeter Guard (PG) module is a hardware (HW) module that can be used to share HW modules between isolated domains, without compromising the isolation itself. PG achieves this by (1) controlling which SoC interconnect master / application can access the protected HW module and by (2) managing the HW module's state during domain switching (i.e. when the HW access get handed over from one application to another), to ensure no unwanted information flows occur.                                    | A prototype implementation, which supports<br>a lock-release with time-sharing operation<br>mode, is available as part of the current<br>implementation of the CROSSCON SoC.<br>The development of additional modes of<br>operation and arbitration is currently<br>ongoing, and additional tests are being<br>performed to extend the range of HW<br>modules the PG can be applied to.                                                                                                | The current implementation of the<br>PG module has successfully been<br>integrated into the CROSSCON SoC,<br>and can be used to limit access to the<br>Static Random-Access Memory<br>(SRAM) HW module.                                      |

| Document name: | D5.2 Integrated CROSSCON Security Stack - First Version |                       |    |          | Page: | 12 of 33 |       |

|----------------|---------------------------------------------------------|-----------------------|----|----------|-------|----------|-------|

| Reference:     | D5.2                                                    | <b>Dissemination:</b> | PU | Version: | 1.0   | Status:  | Final |

<sup>&</sup>lt;sup>1</sup> Description of CROSSCON SoC (chapter 2.2 of D4.2[7])

#### 2.2 Status of CROSSCON Stack Trusted Services

Table 2 provides an overview of each of the CROSSCON Stack trusted services' development progress, including a description of the service, its current integrability into the use case setups and a demonstration of its current technical capabilities, where available. For a more detailed description regarding each of the trusted services, please refer to section 3.3 of D3.1[4]. For an overview of the code used for the technical demonstrations, please refer to D3.2[5] and D4.2[7].

| Trusted Service                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Current Integration Status                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Technical Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUF-based<br>authentication     | CROSSCON aims to innovate and integrate a<br>secure, efficient, lightweight and scalable<br>PUF-based authentication scheme,<br>facilitating resource-constraint embedded<br>devices to authenticate themselves between<br>each other, based on their inherent<br>hardware variations. During the project,<br>three main implementation methods have<br>been identified:<br><b>ZK-PUF:</b> PUF-based authentication via<br>zero-knowledge proofs,<br><b>PAVOC:</b> PUF-based authentication via<br>one-way chains, and<br><b>PAWOS:</b> PUF-based authentication via<br>one-time signatures. | All three of the proposed PUF-based<br>authentication schemes have been<br>implemented and tested on the NXP<br>LPC55S6x hardware board, as part of the<br>integration efforts for UC1. This<br>implementation shows the compatibility of<br>the trusted service with a virtualization-less<br>deployment of the CROSSCON Stack.<br>We are currently working on integrating the<br>PUF-based authentication mechanisms into<br>the CROSSCON Stack as a Trusted<br>Application (TA) | <ul> <li>The three implementations on the LPC55S6x hardware board are able to demonstrate both of the operational phases of PUF-based authentications</li> <li>Enrollment: The systems correctly generated the public data from the PUF responses of the IoT device.</li> <li>Authentication: The verification device is able to correctly verify the authenticity of the IoT device using its PUF responses and the public data.</li> </ul> |

| Context-based<br>authentication | As an additional authentication method, a context-based authentication scheme is being developed, which utilizes the Wi-Fi landscape around a device to provide it with                                                                                                                                                                                                                                                                                                                                                                                                                      | A first implementation of the context-based<br>authentication has been implemented on<br>the RPi 4B board, which was able to collect<br>samples of the metadata of the Wi-Fi                                                                                                                                                                                                                                                                                                       | Not available                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### Table 2: Progress overview of CROSSCON Stack trusted services

| Document name: | D5.2 Integrated C | Page:             | 13 of 33 |     |         |       |

|----------------|-------------------|-------------------|----------|-----|---------|-------|

| Reference:     | D5.2              | Dissemination: PU | Version: | 1.0 | Status: | Final |

|              | a unique fingerprint. This fingerprint can be<br>used to authenticate the device to an<br>authoritative party, based on Siamese<br>networking and machine learning to validate<br>the similarity between a submitted and<br>enrolled fingerprint of the networking<br>landscape of the device.                                                                                  | landscape required for fingerprint<br>generation. Tests are currently ongoing to<br>expand its compatibility with other<br>hardware platforms.<br>In addition, first experiments with the<br>Siamese networking have been performed,<br>but further testing is required before it can<br>be integrated and validated as a trusted<br>service. |                                                                                                                                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secure FPGA  | The secure FPGA provisioning service of the CROSSCON Stack will allow its clients to deploy and operate remote shared FPGA hardware platforms, while at the same time ensuring (1) the confidentiality of the proprietary FPGA workloads and designs, and (2) protection against malicious workloads from other users and/or malicious logic insertions into the design itself. | Although the secure FPGA provisioning<br>service is still in development, an important<br>step toward has been made regarding the<br>design and implementation of the FPGA<br>shell in the FPGA fabric. This shell will be<br>responsible for configuring the rest of the<br>setup at runtime.                                                | The current prototype of the secure<br>FPGA provisioning service is able to<br>reconfigure two virtual FPGAs at<br>runtime with different accelerators<br>through the internal configuration port. |

| provisioning | <ul> <li>It achieves this by provided two main subservices:</li> <li>FPGA Configuration service: Which is responsible for securely deploying and configuring a user's FPGA design onto a remote FPGA hardware module.</li> <li>FPGA Bitstream Scanning service: Which is responsible for ensuring the user's designs are free from</li> </ul>                                   |                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                    |

| Document name: | Document name: D5.2 Integrated CROSSCON Security Stack - First Version |                       |    |          |     |         |       |  |

|----------------|------------------------------------------------------------------------|-----------------------|----|----------|-----|---------|-------|--|

| Reference:     | D5.2                                                                   | <b>Dissemination:</b> | PU | Version: | 1.0 | Status: | Final |  |

|                                                  | malicious circuits before being deployed on the FPGA device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Behavioral-based<br>network anomaly<br>detection | A network anomaly detection service is<br>being developed, which will monitor the<br>networking activities of an embedded<br>device, and detect any deviations from its<br>regular behavior. These deviations include,<br>but are not limited to, suspicious port<br>numbers being exposed by the device, or<br>suspicious communication and/or protocols<br>being used with other devices or IP<br>addresses.                                                                                                                                                                                                                                                                                                            | The behavioral-based network anomaly<br>detection service implementation of the<br>CROSSCON Stack is currently still under<br>development. Once the service is ready, it<br>will be integrated into the CROSSCON Stack<br>as a Trusted Application (TA).                               | Not available                                                                                                                                                                                                                                                                                                        |

| Control flow<br>integrity                        | CROSSCON aims to extend protection<br>against control flow attacks, i.e. attacks<br>aimed at diverting the sequence of executed<br>instructions of an application, to IoT devices<br>that either lack or are not compatible with<br>existing hardware-specific solutions.<br>Two control flow integrity service<br>implementations, protecting either the<br>backwards edge, ensuring that each<br>function returns to the point in the code<br>where it was called, and/or the forwards<br>edge of the control flow, ensuring the<br>destination address of the execution is part<br>of a set of allowed destinations, are<br>developed:<br><b>Flashadow:</b> backwards edge control<br>flow protection for the CROSSCON | A first implementation of both the<br>Flashadow and uIPS control flow<br>mechanisms have been integrated onto the<br>CROSSCON bare metal TEE for non-MPU<br>and MPU hardware modules, respectively.<br>More testing is currently ongoing to further<br>validate these implementations. | The current implementation for both<br>MPU and non-MPU devices are able to<br>demonstrate the ability to protect the<br>forward and backward edges (where<br>applicable) of the control flow, detecting<br>unsafe deviations from the original<br>sequence of operations and halting the<br>execution in such cases. |

| Document name: | D5.2 Integrated C | ROSSCON Securit       | Page: | 15 of 33 |     |         |       |

|----------------|-------------------|-----------------------|-------|----------|-----|---------|-------|

| Reference:     | D5.2              | <b>Dissemination:</b> | PU    | Version: | 1.0 | Status: | Final |

|                                      | non-MPU bare metal TEE (designed<br>for Class 0 devices, as defined in<br>D1.5[2])<br><b>uIPS:</b> backwards and forwards edge<br>control flow protection for the<br>CROSSCON MPU bare metal TEE<br>(designed for Class 1 devices, as<br>defined in D1.5[2])                                                                                                                                                                                |                                                                                                                                                                                                                        |               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Remote attestation                   | Remote attestation is an existing security<br>mechanism that allows a device to verify the<br>integrity and authenticity of another remote<br>device, ensuring it has not been<br>compromised or tampered with. CROSSCON<br>aims to enhance the capabilities of regular<br>remote attestation by providing a service<br>that allows users to easily configure and call<br>a remote attestation of one of the VMs<br>running upon its Stack. | The remote attestation implementation of<br>the CROSSCON Stack is currently still under<br>development. Once the service is ready, it<br>will be integrated into the CROSSCON Stack<br>as a Trusted Application (TA).  | Not available |

| ML-based control<br>flow attestation | This service allows the user to utilize remote<br>attestation to verify the integrity of the<br>control flow of a vulnerable and/or security-<br>relevant application, using Unsupervised<br>Graph Neural Networks (GNNs) to detect any<br>deviations from regular operational<br>sequences.                                                                                                                                                | The implementation of the ML-based<br>runtime attestation of the CROSSCON Stack<br>is currently still under development. Once<br>the service is ready, it will be integrated into<br>the CROSSCON SoC as a peripheral. | Not available |

| Document name: | D5.2 Integrated C | ROSSCON Securit       | Page: | 16 of 33 |     |         |       |

|----------------|-------------------|-----------------------|-------|----------|-----|---------|-------|

| Reference:     | D5.2              | <b>Dissemination:</b> | PU    | Version: | 1.0 | Status: | Final |

### 3 Use Case Integration Prototypes

Within Chapter 3, a detailed description of each of the use case implementation prototypes will be provided, split into sections for each use case. In addition to the architecture of the use case integration prototypes, this chapter will highlight the components and trusted services each of the use cases will leverage for increased security, as well as a first integration timeline.

It is important to note that the prototype architectures and integration timelines are subject to changes, depending on the input and development timeline of the CROSSCON Stack, as well as its components and services.

#### 3.1 UC 1 - Device Multi-Factor Authentication

#### 3.1.1 Prototype Architecture

The main goal of UC 1 is to provide a Multi-Factor Authentication (MFA) implementation for lightweight and resource-constraint IoT devices, in order to protect their users from Man-in-the-Middle (MitM) attacks, amongst others. It achieves this by implementing a basic first authentication factor based on a mutual Transport Layer Security (mTLS) TA implementation. For the secondary authentication, the UC will leverage either the PUF-based or Context-based authentication schemes developed as part of the trusted services of the CROSSCON Stack, depending on their availability on the underlying hardware (see Table 1 of D3.1[4] for an overview of the features of each of the hardware platforms considered for CROSSCON).

More specifically, UC 1 aims to provide a MFA implementation for two distinct operational scenarios:

#### 3.1.1.1 Scenario 1: One-way authentication between a low-end and a high-end device

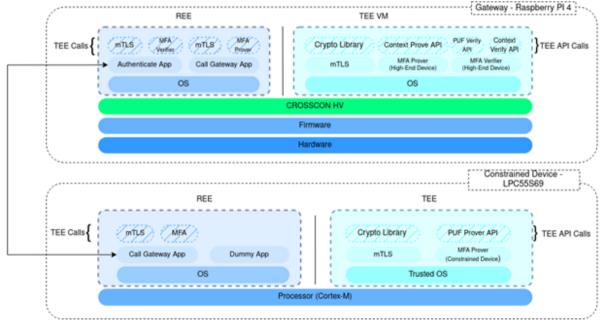

Within the first operational scenario, UC 1 proposes the following implementation to provide a oneway authentication mechanism between the resource-constrained IoT devices and gateways:

Figure 2: MFA implementation prototype for low-end to high-end device authentication

| Document name: | D5.2 Integrated C | Page:                 | 17 of 33 |          |     |         |       |

|----------------|-------------------|-----------------------|----------|----------|-----|---------|-------|

| Reference:     | D5.2              | <b>Dissemination:</b> | PU       | Version: | 1.0 | Status: | Final |

Utilizing the architecture as defined in Figure 2, the following workflow will be implemented:

- 0. The constrained IoT device, based on a NXP LPC55S6x, enrolls its PUF responses to a public database, as described in Section 3.3.1 of D3.1[4], prior to its required authentication.

- 1. The constrained IoT device sends a mTLS request to the gateway, itself based on a Raspberry Pi 4B.

- 2. Once the gateway receives the request from the constrained device, it verifies the provided certificate.

- a. If the certificate is valid, a secure encrypted channel is established between the constrained device and the gateway. The gateway then sends an authentication response to the constrained device, prompting for a second authentication factor.

- b. If the certificate provided by the constrained device is invalid, the gateway sends a negative authentication response and does not prompt for the second authentication factor.

- 3. In case of a successful first authentication, the constrained IoT generates a secondary authentication using its PUF-based MFA implementation, and forwards this to the gateway.

- 4. The gateway verifies the received PUF-based authentication using the aforementioned public data.

- a. If the second factor authentication fails, the gateway sends a negative authentication response back to the IoT device.

- b. If the second factor is valid, the gateway sends a positive authentication response.

#### 3.1.1.2 Scenario 2: Mutual authentication between two high-end devices

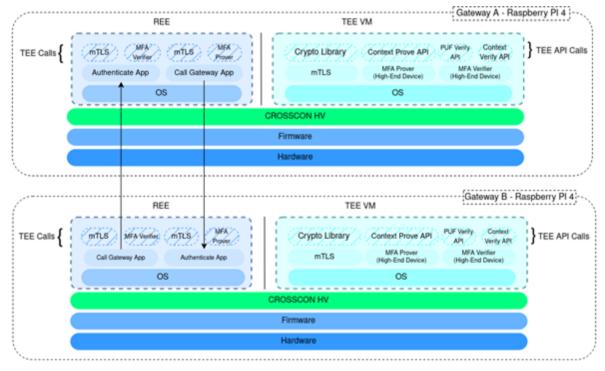

Where the first scenario focuses on the one-way authentication of a low-end to a high-end device, the second scenario explores the possibility to provide a more complex, mutual authentication between two high-end devices. The proposed implementation architecture can be found in Figure 3:

Figure 3: MFA implementation prototype for mutual authentication between two high-end devices

| Document name: | D5.2 Integrated C | ROSSCON Securit       | Page: | 18 of 33 |     |         |       |

|----------------|-------------------|-----------------------|-------|----------|-----|---------|-------|

| Reference:     | D5.2              | <b>Dissemination:</b> | PU    | Version: | 1.0 | Status: | Final |

As the high-end gateway devices are more powerful and have extended capabilities compared to the low-end devices of the first scenario, the MFA will be based on context-based, rather than PUF-based authentication, as described in the following workflow:

- 0. Both Gateway A and Gateway B, each based on a Raspberry Pi 4B hardware module, have enrolled their Wi-Fi landscape fingerprints with each other, in order to be able to validate each other's Context-based MFA.

- 1. Gateway A sends a mTLS request to Gateway B.

- 2. Once Gateway B receives the authentication request, it verifies the provided certificate.

- a. If the certificate is valid, a secure encrypted channel is established between the two gateways. Gateway B then sends an authentication response to Gateway A, prompting for a second authentication factor.

- b. If the certificate provided by Gateway A is invalid, Gateway B sends a negative authentication response and does not prompt for the second authentication factor.

- 3. In case of a successful first authentication, the Gateway A generates a secondary authentication using its Context-based MFA implementation, and forwards this to Gateway B.

- 4. Gateway B verifies the Context-based authentication using the Siamese network implementation of the MFA TA.

- a. If the second factor is invalid, Gateway B sends a negative authentication response.

- b. If the second factor is valid, the Gateway B sends a positive authentication response, and provides its own secondary Context-based authentication factor to Gateway A.

- 5. Gateway A verifies the received Context-based authentication from Gateway B using its own Siamese network.

- a. If the second factor is invalid, Gateway A sends a negative authentication response.

- b. If the second factor is valid, Gateway A returns a positive authentication response.

#### 3.1.2 Required Security Features

The integration and operation of the two architectures described before will leverage the following security features, obtained from the components and trusted services of the CROSSCON Stack:

- **CROSSCON Hypervisor support on hardware platforms:** The implementations of both the first and second operational scenario of UC 1 are designed to operate using the CROSSCON Hypervisor on top of either a NXP LPC55S6x or Raspberry Pi 4B hardware platform. However, as described in Section 2.1, the CROSSCON Hypervisor is currently only compatible with QEMU, and efforts to ensure its compatibility with the required hardware platforms are ongoing.

- **PUF-Based Authentication Prover API for Low-End devices:** An API will have to be developed for the PUF-based authentication implementation on low-end devices, such that they can generate PUF responses whenever a MFA is required.

- **PUF-Based Authentication Verifier API for High-End devices:** An API will have to be developed for the PUF-based authentication implementation on high-end devices, such that they can validate the PUF-based authentication of low-end devices, when requested.

- **Context-Based Authentication Prover & Verifier API for High-End devices:** An API will have to be developed for the Context-based authentication implementation on high-end devices, such that they can both (1) generate their Wi-Fi landscape fingerprint, and (2) validate the Wi-Fi landscape fingerprint of another high-end device, when requested.

#### 3.1.3 Integration Timeline

Considering the proposed implementation architectures and operational scenarios, as well as the ongoing development of the CROSSCON Stack, the following integration timeline is predicted for the use case prototype:

|                                                            | 2024 |   |   | 2025 |    |    |   |   |   |   |   |   |   |   |   |    |

|------------------------------------------------------------|------|---|---|------|----|----|---|---|---|---|---|---|---|---|---|----|

| Integration Activity                                       | 7    | 8 | 9 | 10   | 11 | 12 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| Integration of the CROSSCON<br>Stack on Raspberry Pi 4B    |      |   |   |      |    |    |   |   |   |   |   |   |   |   |   |    |

| Integration of the CROSSCON authentication implementations |      |   |   |      |    |    |   |   |   |   |   |   |   |   |   |    |

| Integration of the MFA application                         |      |   |   |      |    |    |   |   |   |   |   |   |   |   |   |    |

| Testing and validation activities                          |      |   |   |      |    |    |   |   |   |   |   |   |   |   |   |    |

| Preparation of final demonstrator                          |      |   |   |      |    |    |   |   |   |   |   |   |   |   |   |    |

#### Table 3: Integration timeline for UC 1

| Document name: | D5.2 Integrated C | ROSSCON Securit       | Page: | 20 of 33 |     |         |       |

|----------------|-------------------|-----------------------|-------|----------|-----|---------|-------|

| Reference:     | D5.2              | <b>Dissemination:</b> | PU    | Version: | 1.0 | Status: | Final |

### 3.2 UC 2 - Firmware Updates of IoT Devices

#### 3.2.1 Prototype Architecture

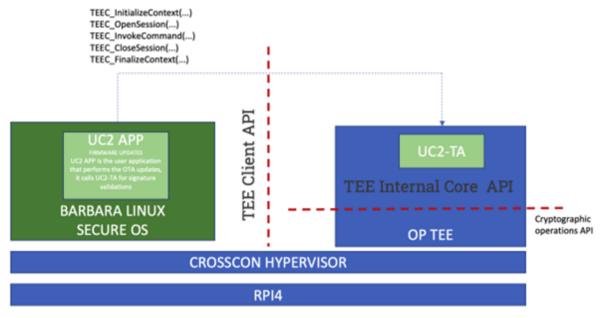

The integration prototype architecture for the UC2, focussing on a secure Over-the-Air (OTA) firmware update implementation lead by BIOT, is the following:

#### Figure 4: Secure firmware update implementation prototype

As depicted in Figure 4, Barbara Secure OS will be deployed inside a VM on top of the CROSSCON Hypervisor, operating on a Raspberry Pi 4B hardware platform. Within the Barbara VM, the UC2 operational application (UC2 APP) will be deployed, which will be responsible for performing the OTA firmware updates. It leverages an external update server<sup>2</sup> to provide the required materials to execute the OTA updating operations.

The UC2 application will utilize a specialized Trusted Application, called UC2-TA, responsible for validating the signature of the downloaded firmware file, using the TEE client API[10]. This TA is deployed on OP-TEE, a TEE instance operating on top of the CROSSCON Hypervisor. Afterwards, the UC2-TA application will utilize the TEE internal Core API[11], in order to perform its critical cryptographic functions.

The operational workflow of UC 2 will be the following:

- 0. An Operating System update image will be generated and stored in the dedicated update server.

- 1. The UC2 OTA will ask the CROSSCON API for a unique ID. This ID will be stored on the device using a secure storage area, provided by the OP-TEE implementation operating on top of the CROSSCON Hypervisor.

- 2. The CROSSCON Stack will be used to set up the secure communication channel between the IoT device and the update server, and the OS update image will be downloaded as an encrypted binary file.

- 3. The UC2-TA application will verify the signature of the encrypted binary file, using the TEE cryptographic operations.

- 4. If the signature is valid, the UC2-TA application will decrypt the update image file using the TEE cryptography operations provided by the TEE API.

<sup>&</sup>lt;sup>2</sup> This server will be deployed and operated independently of the aforementioned implementation prototype, not requiring integration with the CROSSCON Stack, and has therefore been omitted from the detailed architecture of Figure 4.

| Document name: | D5.2 Integrated C | Page:                 | 21 of 33 |          |     |         |       |

|----------------|-------------------|-----------------------|----------|----------|-----|---------|-------|

| Reference:     | D5.2              | <b>Dissemination:</b> | PU       | Version: | 1.0 | Status: | Final |

#### 3.2.2 Required Security Features

The integration and operation of the two architectures described before will leverage the following security features, obtained from the components and trusted services of the CROSSCON Stack:

- **CROSSCON Hypervisor support on RPI4:** The architecture of UC 2 is designed to operate using the CROSSCON Hypervisor on top of a Raspberry Pi 4B hardware platform. However, as described in Section 2.1, the CROSSCON Hypervisor is currently only compatible with QEMU, and efforts to ensure its compatibility with the Raspberry Pi 4B hardware platform are ongoing.

- **CROSSCON TEE implementation:** The UC2-TA application requires to be deployed on a OP-TEE implementation on top of the CROSSCON Hypervisor, as the TA will leverage the TEE implementation to (1) provide the secure storage capabilities, (2) allow for the generation of a unique identifier and (3) perform the cryptographic operations required for the use case.

- Unique identifier (ID) provisioning: The OTA firmware update application requires a unique device ID to be provisioned by the CROSSCON Stack. The implementation of this service is not considered as a trusted service, but will instead leverage the secure storage capabilities of the CROSSCON TEE implementation to generate and store the unique ID.

- Secure storage capability: The CROSSCON Stack will provide the ability to allocate secure storage to store sensitive data (e.g. cryptographic keys, unique ID, etc.) only accessible by allowed applications.

- Secure Communication Channel: To ensure the authenticity, integrity and confidentiality of the communication between the IoT device and the firmware update server, a method to establish a secure communication channel will have to be available.

#### 3.2.3 Integration Timeline

At first, the integration of the prototype into the testbed will be performed, which will serve as a first evaluation of the CROSSCON Stack, and provide feedback to the developers of WP2, 3 and 4. The integration schedule of this first implementation is presented in Table 4, and has been divided in three integration phases:

- 1. Development of the emulated environment setup, where we can begin creating and running the Hypervisor, the TEE and Barbara OS on top of CROSSCON Hypervisor.

- 2. Development of UC2-TA, and its integration within the CROSSCON TEE environment

- 3. Development of the UC2 OTA update application, its integration within the Barbara OS VM and the establishment of the communication between the UC2 OTA update application and the UC2-TA.

After the integration, a continuous testing and integration framework will be implemented, in order to continue validating the advancements made, and to provide feedback to the development of the CROSCONN Stack.

|                                                  |   |   | 20 | 24 |    |    |   |   |   |   | 20 | 25 |   |   |   |    |

|--------------------------------------------------|---|---|----|----|----|----|---|---|---|---|----|----|---|---|---|----|

| Integration Activity                             | 7 | 8 | 9  | 10 | 11 | 12 | 1 | 2 | 3 | 4 | 5  | 6  | 7 | 8 | 9 | 10 |

| Development of the emulated<br>environment setup |   |   |    |    |    |    |   |   |   |   |    |    |   |   |   |    |

| Development of UC2-TA                            |   |   |    |    |    |    |   |   |   |   |    |    |   |   |   |    |

| Development of the UC2 OTA update application    |   |   |    |    |    |    |   |   |   |   |    |    |   |   |   |    |

| Continuous Testing and validation activities     |   |   |    |    |    |    |   |   |   |   |    |    |   |   |   |    |

| Preparation of final<br>demonstrator             |   |   |    |    |    |    |   |   |   |   |    |    |   |   |   |    |

#### Table 4: Integration timeline for UC 2

| Document name: | D5.2 Integrated ( | CROSSCON Security Stack - First Version |          |     | Page:   | 22 of 33 |

|----------------|-------------------|-----------------------------------------|----------|-----|---------|----------|

| Reference:     | D5.2              | Dissemination: PU                       | Version: | 1.0 | Status: | Final    |

#### 3.3 UC 3 – Commissioning and Decommissioning of IoT Devices

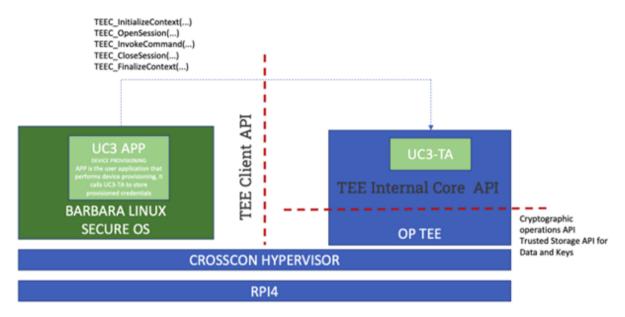

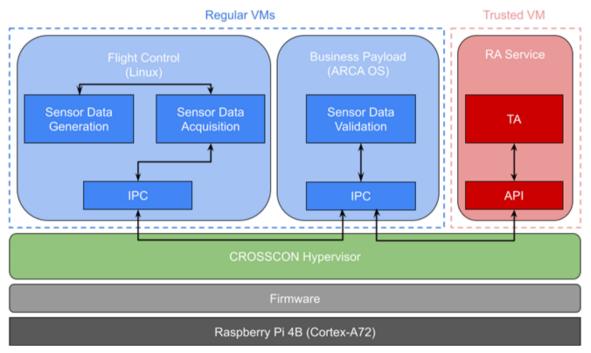

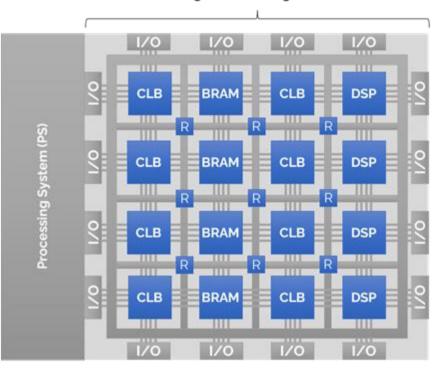

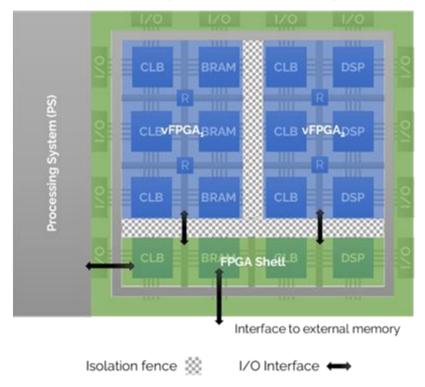

#### 3.3.1 Prototype Architecture